如果你(妳)對此文有意見、問題或興趣,請和我們聯絡:

Email: cometrue@icometrue.com

第四課: 我的摩爾人生

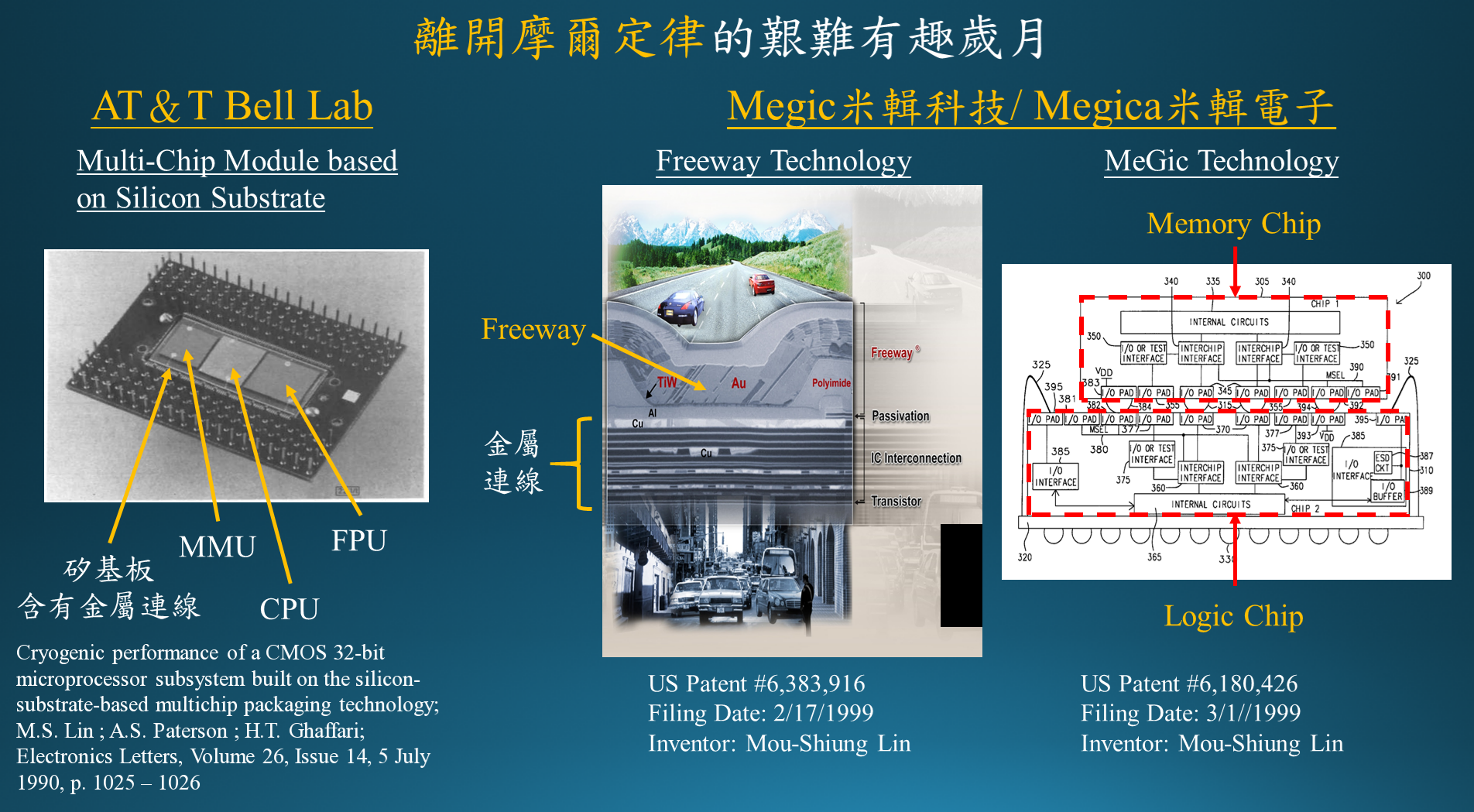

我在半導體產業四十年,沈浮在摩爾定律的浪潮中:曾經兩度進入摩爾定律的浪潮,也兩度退出轉而發展非摩爾定律的技術。1982-1984年我任職於IBM,參與開發了第一代CMOS 1 (1.0 微米)和第二代CMOS 2 (0.8 微米)製程。1985-1990期間,因預測曝光技術將在0.1- 0.2 微米時達到光波解析度的物理極限,決定離開摩爾定律的浪潮,加入了AT&T Bell Labs開發矽基板上的多晶片模組 (Multi-chip module MCM based on silicon substrate)技術。AT&T Bell Labs在1984-1988年間投資了3億美元,網羅跨領域(系統及晶片)近百位人才去開發MCM技術,可惜早了30多年。台積電現在的CoWoS(Chip-on-Wafer-on-Substrate)就類似當年AT&T Bell Labs 的MCM技術。AT&T Bell Labs 在30多年前投入MCM技術研發,開發了在矽晶圓上電鍍銅金屬連線的電鍍技術,開啓了矽晶圓上電鍍製程技術的研發,成為現今半導體電鍍銅金屬連線主流製程技術的先驅。1990-1995年間我回到摩爾定律的浪潮,帶領著台積電的研發團隊,開發從0.8到0.35微米八代的製程技術。而後於1999-2011期間再次離開摩爾定律,創辦了米輯科技(Megic)和米輯電子(Megica),提倡MeGic技術。”MeGic”是”Me”mory和lo”Gic”合成的字,而中文”米輯”的”米”是指如稻米大宗商品(Commodity)一樣的記憶晶片,”輯”則是指邏輯晶片的輯。MeGic技術是把memory晶片和logic晶片正面對正面堆疊聯結在一起,增加電晶體數目及運算速度。可惜這個技術開發的太早,在當時並沒有成功。可是到了2016年,台積電和Intel都開始研發memory晶片和logic晶片正面對正面堆疊聯結的技術。

值得一提的是,全球最大的智慧型手機通訊晶片公司在2009年購買了米輯電子公司,主要是全球有一家電腦公司的CPU晶片在2007年用到了米輯電子公司發明的Freeway技術專利。晶片遵循摩爾定律,金屬連線越做越窄越薄,雖然密度很高,可以連接到晶片上的每一個電晶體;但電阻電容高,速度慢,就好比台北市內的道路可以通往每一個地點,可是車子擁擠,又有紅綠燈,因此速度慢。我當時想,為什麼不把當年在AT&T Bell Labs的5微米厚的電鍍銅技術直接做在晶圓最上層的保護層(Passivation Layer)上面呢?這就是米輯提倡並取名的Freeway技術。Freeway技術5 微米的金屬連線可以提供晶片高速連線,如果要到比較遠的地方,就必須上高速公路 (Freeway)。Freeway技術的金屬連線越做越寛越厚,可以説是反摩爾定律(Reverse Moore’s Law)。Freeway提供了新的晶片設計架構 - Freeway Architecture。米輯當時在美國和台灣就註冊了FREEWAY的商標。2009年7月,當我和這家智慧型手機通訊晶片公司完成公司買賣合約簽訂時,心裡非常興奮,感覺上好像台灣賣核子彈給美國一樣。

歷經40年二進二出摩爾定律的歲月,在摩爾定律及非摩爾定律之間,現在的我是如何抉擇呢?如前所述,我在2016年提出邏輯硬碟的概念,把摩爾定律及非摩爾定律結合在一起。一方面,利用摩爾定律的神奇魔力,應用10奈米以下先進製程製作的標準大宗FPGA晶片所提供的超過百億個高效能、低耗電電晶體;另一方面,利用非摩爾定律的先進微縮的多晶片封裝技術,將多顆標準大宗FPGA晶片與一些輔助及協同晶片封裝在一個包裝內,以倍數增加電晶體的數目。有趣的是,先進的多晶片封裝的尺寸微縮(Miniaturization)過程也走上像晶片發展一樣的摩爾定律老路:每單位面積或體積內的電晶體數目逐年不斷的增加。

(本文係依據林董事長刊登於2021年11月18日電子時報專欄的文章修訂而成。)

電子時報連結: 第四課